# Bit-Sliced Microprocessor of the Am2900 Family: The Am2901/2909<sup>1</sup>

#### Introduction

### The Am2900 Family

The Am2900 Family consists of a series of LSI building blocks designed for use in microprogrammed computers and controllers. Each device is designed to be expandable and sufficiently flexible to be suitable for emulation of many existing machines.

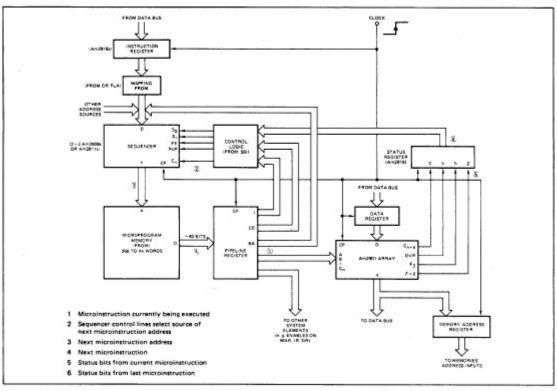

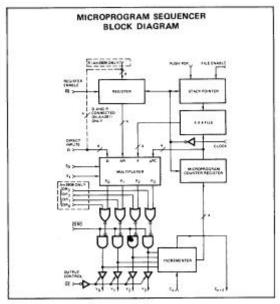

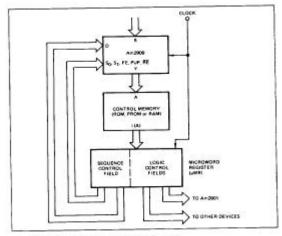

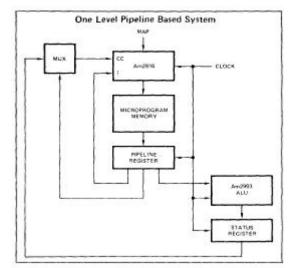

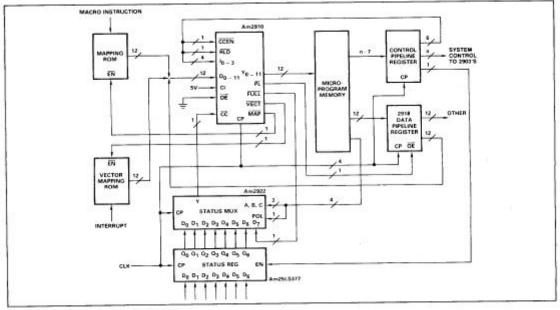

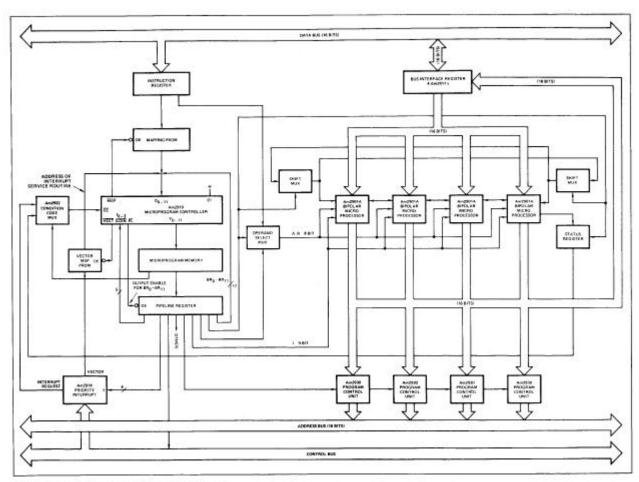

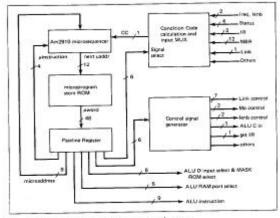

Figure 1 illustrates a typical system architecture. There are two "sides" to the system. At the left is the control circuitry and on the right is the data manipulation circuitry. The block labeled "2901 array" consists of the ALU, scratchpad registers, and data steering logic (all internal to the Am2901's), plus left/right shift control and carry lookahead circuit. Data is processed by moving it from main memory (not shown) into the 2901 registers, performing the required operations on it, and returning the result to main memory. Memory addresses may also be generated in the 2901's and sent out to the memory address register (MAR). The four status bits from the 2901's ALU are captured in the status register after each operation.

The logic on the left side is the control section of the computer. This is where the Am2909 is used. The entire system is controlled by a memory, usually PROM, which contains long words called microinstructions. Each microinstruction contains bits to control each of the data manipulation elements in the system. There are, for example, 9 bits for the 2901 instruction lines, 8 bits for the A and B register addresses, 2 or 3 bits to control the shifting multiplexers at the ends of the 2901 array, and bits to control the register enables on the MAR, instruction register, and various bus transceivers. When the bits in a microinstruction are applied to all the data elements and everything is clocked, then one small operation (such as a data transfer or a register-to-register add) will occur.

Each microinstruction contains not only bits to control the data hardware, but also bits to define the location in PROM of the next microinstruction to be executed. The fields are labeled in Fig. 1 as I, CC, and BA. The I field controls the sequencer. It indicates where the next address is located-the  $\mu$  PC, the stack, or the direct inputs-and whether the stack is to be pushed or popped.

The CC field contains bits indicating the conditions under which the I field applies. These are compared with the condition codes in the status register and may cause modification to the I field. The comparing and modification occurs in the block labeled "control logic." Frequently this is just a PROM. The BA field is a branch address or the address of a subroutine.

### Pipelining

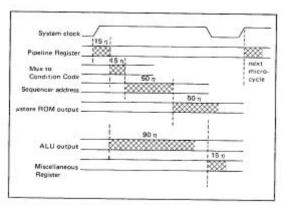

The address for the microinstructions is generated by the sequencer, starting from a clock edge. The address goes from the sequencer to the ROM, and an access time later, the microinstruction is at the ROM outputs.

A pipeline register is a register placed on the output of the microprogram memory to essentially split the system in two. The pipeline register contains the microinstruction currently being executed  $\neg$ . (Refer to the circled numbers in Fig. 1.) The data manipulation control bits go out to the system elements and a portion of the microinstruction is returned to the sequencer to determine the address of the next microinstruction to be executed. That address ® is sent to the ROM, and the next microinstruction  $\neg$  sits at the input of the pipeline register. So while the 2901's are executing one instruction, the next instruction is being fetched from ROM. Note that there is no sequential logic in the sequencer between the select lines and the output. This is important because the loop  $\neg$  to  $\nabla$  must occur during a single clock cycle. During the same time, the loop from  $\neg$  to  $^{\circ}$  must occur in the 2901's. These two paths are roughly the same (around 200 ns worst case for a 16-bit system). The presence of the pipeline register allows the microinstruction fetch to occur in parallel with the data operation rather than serially, allowing the clock frequency to be doubled.

The emulation of an existing machine by Fig. 1 works as follows. A sequence of microinstructions in the PROM is executed to fetch an instruction from main memory. This requires that the program counter, often in a 2901 working register, be sent to the memory address register and incremented. The data returned from memory is loaded into the instruction register. The contents of the instruction register are passed through a PROM or PLA to generate the address of the first microinstruction which must be executed to perform the required function. A branch to this address occurs through the sequencer. Several microinstructions may be executed to fetch data from memory, perform ALU operations, test for overflow, and so forth. Then a branch will be made back to the instruction fetch cycle. At this point, there may be branches to other sections of microcode. For example, the machine might test for an interrupt here and obtain an interrupt service routine address from another mapping ROM rather than start on the next machine instruction.

<sup>1</sup>Abstracted from *The Am2DOO Family Data Book*, Advanced Micro Devices, Inc., 1976.

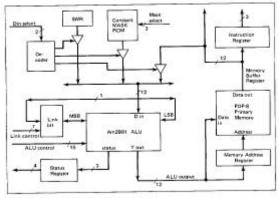

#### Am2901: Four-Bit Bipolar Microprocessor Slice

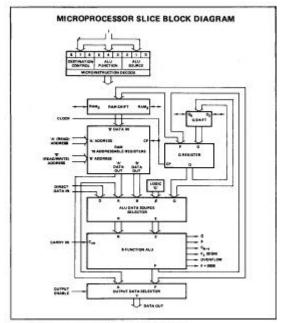

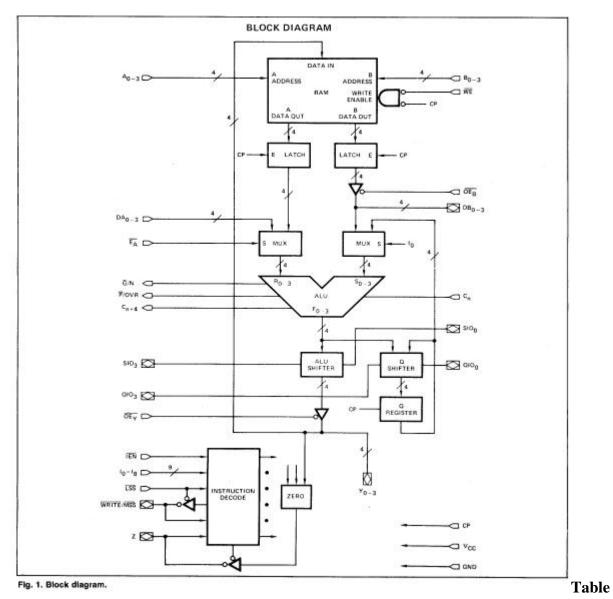

The device, as shown in Fig. 2, consists of a 16-word by 4-bit two-port RAM, a high-speed ALU, and the associated shifting, decoding, and multiplexing circuitry. The 9-bit microinstruction word is organized into three groups of 3 bits each and selects the ALU source operands, the ALU function, and the ALU destination register. The microprocessor is cascadable with full lookahead or with ripple carry, has three-state outputs, and provides various status flag outputs from the ALU. Advanced low-power Schottky processing is used to fabricate this 40-lead LSI chip.

#### Architecture

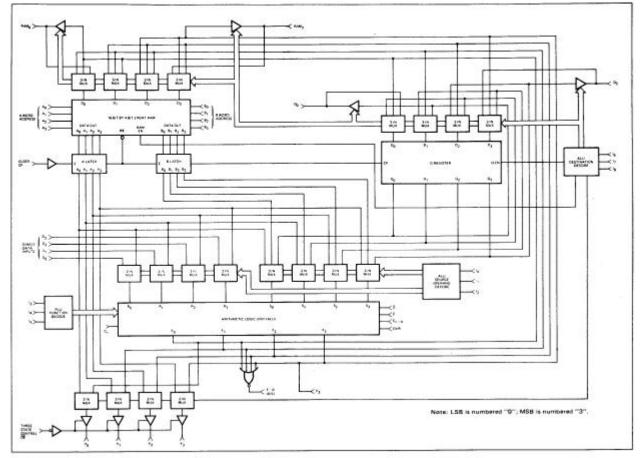

A detailed block diagram of the bipolar microprogrammable microprocessor structure is shown in Fig. 3. The circuit is a 4-bit slice cascadable to any number of bits, Therefore, all data paths within the circuit are 4 bits wide. The two key elements in the Fig. 3 block diagram are the 16-word by 4-bit two-port RAM and the high-speed ALU.

Data in any of the 16 words of the random-access memory (RAM) can be read from the A port of the RAM as controlled by the 4-bit A address field input. Likewise, data in any of the 16 words of the RAM as defined by the B address field input can be

Fig. 2. Microprocessor slice block diagram.

simultaneously read from the B port of the RAM. The same code can be applied to the A select field and B select field, in which case the identical file data will appear at both the RAM A port and B port outputs simultaneously.

When enabled by the RAM write enable (RAM EN), new data is always written into the field (word) defined by the B address field of the RAM. The RAM data-input field is driven by a three-input multiplexer. This configuration is used to shift the ALU output data (F) if desired. This three-input multiplexer scheme allows the data to be shifted up one bit position, shifted down one bit position, or not shifted in either direction.

The RAM A port data outputs and RAM B port data outputs drive separate 4-bit latches. These latches hold the RAM data while the clock input is LOW. This eliminates any possible race conditions that could occur while new data is being written into the RAM.

The high-speed Arithmetic Logic Unit (ALU) can perform three binary arithmetic and five logic operations on the two 4-bit words R and S. The R input field is driven from a two-input multiplexer, while the S input field is driven from a three-input multiplexer. Both multiplexers also have an inhibit capability; that is, no data is passed. This is equivalent to a zero source operand.

In Fig. 3, the ALU R-input multiplexer has the RAM A port and the direct data inputs (D) connected as inputs. Likewise, the ALU S-input multiplexer has the RAM A port, the RAM B port, and the Q register connected as inputs.

The two source operands not fully described as yet are the D input and Q input. The D input is the 4-bit-wide direct data-field input. This port is used to insert all data into the working registers inside the device. Likewise, this input can be used in the ALU to modify any of the internal data files. The Q register is a separate 4-bit file intended primarily for multiplication and division routines, but **it** can also be used as an accumulator or holding register for some applications.

This multiplexer scheme gives the capability of selecting various pairs of the A, B, D, Q, and O inputs as source operands to the ALU. These five inputs, when taken two at a time, result in ten possible combinations of source operand pairs. These combinations include AB, AD, AQ, AO, BD, BQ, BO, DQ, DO, and QO. It is apparent that AD, AQ, and AO are somewhat redundant with BD, BQ, and BO in that if the A address and B address are the same, the identical function results. Thus, there are only seven completely non-redundant source operand pairs for the ALU. The Am2901 microprocessor implements eight of these pairs. The microinstruction inputs used to select the ALU source operands are the I<sub>0</sub>, I<sub>1</sub>, and I<sub>2</sub> inputs. The definitions of I<sub>0</sub>, I<sub>1</sub>, and I<sub>2</sub> for the eight source operand combinations are as shown in Table1. Also shown is the octal code for each selection.

The  $I_3$ ,  $I_4$ , and  $I_5$  microinstruction inputs are used to select the ALU function. The definition of these inputs is shown in Table 2. The octal code is also shown for reference. The normal technique for cascading the ALU of several devices is in a lookahead carry mode. Carry generate, G, and carry propagate, P, are outputs of the device for use with a carry-lookahead generator such as the

#### **Table 1 ALU Source Operand Control**

|       | Micro | ALU source operands |            |   |   |

|-------|-------|---------------------|------------|---|---|

| $I_2$ | $I_1$ | 10                  | Octal code | R | S |

| L     | L     | L                   | 0          | A | Q |

| L     | L     | Н                   | 1          | A | В |

| L     | Н     | L                   | 2          | 0 | Q |

| L | Н | Н | 3 | 0 | В |

|---|---|---|---|---|---|

| Н | L | L | 4 | 0 | A |

| Н | L | Н | 5 | D | A |

| Н | Н | L | 6 | D | Q |

| Н | Н | Н | 7 | D | 0 |

Fig. 3. Detailed Am2901 microprocessor block diagram.

|       | M     | licroco | de         | ALU function | Symbol |

|-------|-------|---------|------------|--------------|--------|

| $I_5$ | $I_4$ | $I_3$   | Octal code |              |        |

| L     | L     | L       | 0          | R plus S     | R+S    |

| L     | L     | Η       | 1          | S minus R    | S–R    |

| L     | Н     | L       | 2          | R minus S    | R–S    |

| L     | Η     | Η       | 3          | R OR S       | R V S  |

| Η     | L     | L       | 4          | R AND S      | RΛS    |

| Η | L | Н | 5 | R AND S    | $R \Lambda S$ |

|---|---|---|---|------------|---------------|

| Η | Н | L | 6 | R EX-OR S  | $R\forall\;S$ |

| Η | Н | Н | 7 | R EX-NOR S | $R \forall S$ |

Am2902 ('182). A carry-out,  $C_{n+4}$ , is also generated and is available as an output for use as the carry flag in a status register. Both carry-in ( $C_n$ ) and carry-out ( $C_{n+4}$ ) are active HIGH.

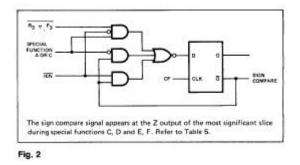

The ALU has three other status-oriented outputs. These are  $F_3$ , F = 0, and overflow (OVR). The  $F_3$  output is the most significant (sign) bit of the ALU and can be used to determine positive or negative results without enabling the three-state data outputs.  $F_3$  is non-inverted with respect to the sign bit output  $Y_3$ . The F = 0 output is used for zero detect. It is an open-collector output and can be wire ORed between microprocessor slices. F = 0 is HIGH when all F outputs are LOW. The overflow output(OVR) is used to flag arithmetic operations that exceed the available 2's complement number range. The overflow output (OVR) is HIGH when overflow exists; that is, when  $C_{n+3}$  and  $C_{n+4}$  are not the same polarity.

The ALU data output is routed to several destinations. It can be a data output of the device and it can also be stored in the RAM or the Q register. Eight possible combinations of ALU destination functions are available as defined by the  $I_6$ ,  $I_7$ , and  $I_8$  microinstruction inputs. These combinations are shown in Table 3.

The 4-bit data output field (Y) features three-state outputs and can be directly bus-organized. An output control (OE) is used to enable the three-state outputs. When OE is HIGH, the Y outputs are in the high-impedance state.

A two-input multiplexer is also used at the data output such that either the A port of the RAM or the ALU outputs (F) are selected at the device Y outputs. This selection is controlled by the  $I_6$ ,  $I_7$ , and  $I_8$  microinstruction inputs. Refer to Table 3 for the selected output for each microinstruction code combination.

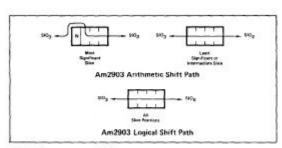

As was discussed previously, the RAM inputs are driven from a three-input multiplexer. This allows the ALU outputs to be entered non-shifted, shifted up one position (multiplied by 2), or shifted down one position (divided by 2). The shifter has two ports; one is labeled RAM<sub>0</sub> and the other is labeled RAM<sub>3</sub>. Both of these ports consist of a buffer-driver with a three-state output and an input to the multiplexer. Thus, in the shift-up mode, the RAM<sub>3</sub> buffer is enabled and the RAM<sub>0</sub> multiplexer input is enabled. Likewise, in the shift-down mode, the RAM<sub>0</sub> buffer and RAM<sub>3</sub> input are enabled. In the no-shift mode, both buffers are in the high-impedance state and the multiplexer inputs are not selected. This shifter is controlled from the I<sub>6</sub>, I<sub>7</sub>, and I<sub>8</sub> microinstruction inputs as defined in Table 3.

|       |       | Micro | code       | RAM f | function            | . –   | egister<br>ction                                    |             | RAM     | shifter          |        | Q<br>fter       |

|-------|-------|-------|------------|-------|---------------------|-------|-----------------------------------------------------|-------------|---------|------------------|--------|-----------------|

| $I_8$ | $I_7$ | $I_6$ | Octal Code | Shift | Load                | Shift | Load                                                | Y<br>output | $RAM_0$ | RAM <sub>3</sub> | $Q_0$  | $Q_3$           |

| L     | L     | L     | 0          | X     | None                | None  | $F \rightarrow Q$                                   | F           | X       | X                | X      | X               |

| L     | L     | Н     | 1          | X     | None                | X     | None                                                | F           | X       | X                | X      | X               |

| L     | Η     | L     | 2          | None  | $F \rightarrow B$   | X     | None                                                | A           | X       | X                | X      | X               |

| L     | Η     | Η     | 3          | None  | $F \rightarrow B$   | X     | None                                                | F           | X       | X                | X      | X               |

| Η     | L     | L     | 4          | Down  | $F/2 \rightarrow B$ | Down  | $\begin{array}{c} Q/2 \rightarrow \\ Q \end{array}$ | F           | $F_0$   | IN <sub>3</sub>  | $Q_0$  | IN <sub>3</sub> |

| Η     | L     | Η     | 5          | Down  | $F/2 \rightarrow B$ | X     | None                                                | F           | $F_0$   | $IN_3$           | $Q_0$  | X               |

| Н     | Η     | L     | 6          | Up    | $2F \rightarrow B$  | Up    | $2Q \rightarrow Q$                                  | F           | $IN_0$  | $F_3$            | $IN_0$ | $Q_3$           |

| Η     | Η     | Η     | 7          | Up    | $2F \rightarrow B$  | X     | None                                                | F           | $IN_0$  | $F_3$            | X      | $Q_3$           |

### **Table 3 ALU Destination Control**

X-Don't care. Electrically, the shift pin is a TTL input internally connected to a three-state output which is in the high impedance state. B-Register Addressed by B inputs.

Up is toward MSB. Down is toward LSB.

Similarly, the Q register is driven from a three-input multiplexer. In the no-shift mode, the multiplexer enters the ALU data into the Q register. In either the shift-up or shift-down mode, the multiplexer selects the Q register data appropriately shifted up or down. The Q shifter also has two ports; one is labeled  $Q_0$  and the other is  $Q_3$ . The operation of these two ports is similar to the RAM shifter and is also controlled from  $I_6$ ,  $I_7$ , and  $I_8$  as shown in Table 3.

The clock input to the Am2901 controls the RAM, the Q register, and the A and B data

latches. When enabled, data is clocked into the Q register on the LOW-to-HIGH transition of the clock. When the clock input is HIGH, the A and B latches are open and will pass whatever data is present at the RAM outputs. When the clock input is LOW, the latches are closed and will retain the last data entered. If the RAM EN is enabled, new data will be written into the RAM file (word) defined by the B address field when the clock input is LOW.

There are eight source operand pairs available to the ALU as selected by the  $I_0$ ,  $I_1$ , and  $I_2$  instruction inputs. The ALU can perform eight functions—five logic and three arithmetic. The  $I_3$ ,  $I_4$ , and  $I_5$  instruction inputs control this function selection. The carry input,  $C_n$ , also affects the ALU results when in the arithmetic mode. The  $C_n$  input has no effect in the logic mode. When  $I_0$  through  $I_5$  and  $C_n$  are viewed together, the matrix of Table 4 results. This matrix fully defines the ALU/source operand function for each state.

The ALU functions can also be examined on a "task" basis, i.e., add, subtract, AND, OR, etc. In the arithmetic mode, the carry will affect the function performed; while in the logic mode, the carry will have no bearing on the ALU output. Table 5 defines the various logic operations that the Am29O1 can perform, and Table 6 shows the arithmetic functions of the device. Both carry-in LOW ( $C_n = 0$ ) and carry-in HIGH ( $C_n = 1$ ) are defined in these operations.

### Logic Functions for G, P, C<sub>n+4</sub>, and OVR

The four signals, G, P,  $C_{n+4}$ , and OVR are designed to indicate carry and overflow conditions when the Am2901 is in the add or subtract mode. Table 7 indicates the logic equations for these four signals for each of the eight ALU functions. The II and S inputs are the two inputs selected according to Table 1.

| Table 4 | Source | Operand | and ALU | Function | Matrix |

|---------|--------|---------|---------|----------|--------|

|---------|--------|---------|---------|----------|--------|

|                  |                                                       |                    |                    | Octal I;<br>ALU so |              |              |                    |                    |              |

|------------------|-------------------------------------------------------|--------------------|--------------------|--------------------|--------------|--------------|--------------------|--------------------|--------------|

| Octal<br>I 5.4.0 | ALU<br>function                                       | 0<br>A, Q          | 1<br>A, B          | 2<br>0, Q          | 3<br>О, В    | 4<br>O, A    | 5<br>D, A          | 6<br>D, Q          | 7<br>D, O    |

| 0                | C <sub>s</sub> = L<br>R plus S<br>C <sub>n</sub> = H  | A + Q<br>A + Q + 1 | A + B<br>A + B + 1 | Q<br>Q + 1         | B<br>B + 1   | A<br>A + 1   | D + A<br>D + A + 1 | D + Q<br>D + Q + 1 | D<br>D + 1   |

| 1                | C, = L<br>S minus R<br>C, = H                         | Q - A - 1<br>Q - A | B – A – 1<br>B – A | Q - 1<br>Q         | B - 1<br>B   | A – 1<br>A   | A – D – 1<br>A – D | Q - D - 1<br>Q - D | -D - 1<br>-D |

| 2                | C <sub>s</sub> = L<br>R minus S<br>C <sub>s</sub> = H | A - Q - 1<br>A - Q | A – B – 1<br>A – B | -Q - 1<br>-Q       | -B - 1<br>-B | -A - 1<br>-A | D – A – 1<br>D – A | D - Q - 1<br>D - Q | D - 1<br>D   |

| 3                | RORS                                                  | . ∧∨Q              | AVB                | Q                  | В            | A            | DVA                | D∨Q                | D            |

| 4                | R AND S                                               | A \ Q              | A $\wedge$ B       | 0                  | 0            | 0            | D 🛆 A              | D \ Q              | 0            |

| 5                | R AND S                                               | Ā A Q              | Ā ∧ B              | Q                  | В            | A            | DΛΑ                | D∧Q                | 0            |

| 6                | R EX-OR S                                             | A₩Q                | A⊹B                | Q                  | В            | A            | D₩A                | D⊹Q                | D            |

| 7                | R EX-NOR S                                            | AVQ                | A→B                | ā                  | B            | Ā            | D₩A                | D₩Q                | D            |

+ = Ptus; - = Minus;  $\lor$  = OR;  $\land$  = AND;  $\nleftrightarrow$  = EX-OR.

| Irrelevant)              | -      |                                                      |

|--------------------------|--------|------------------------------------------------------|

| Octal<br>I 5,4, 1 2, 1,0 | Group  | Function                                             |

| 4 0<br>4 1<br>4 5<br>4 6 | AND    | A \ Q<br>A \ B<br>D \ A<br>D \ Q                     |

| 3 0<br>3 1<br>3 5<br>3 6 | OR     | A \ Q<br>A \ B<br>D \ A<br>D \ Q                     |

| 6 0<br>6 1<br>6 5<br>6 6 | EX-OR  | A - ∀ Q<br>A - ∀ B<br>D - ∀ A<br>D - ∀ Q             |

| 70<br>71<br>75<br>76     | EX-NOR | $A \neq Q$<br>$A \neq B$<br>$D \neq A$<br>$D \neq Q$ |

| 72<br>73<br>74<br>77     | INVERT | 10 BIAID                                             |

| 62<br>63<br>64<br>67     | PASS   | Q<br>B<br>A<br>D                                     |

| 3 2<br>3 3<br>3 4<br>3 7 | PASS   | Q<br>B<br>A<br>D                                     |

| 4 2<br>4 3<br>4 4<br>4 7 | "ZERO" | 0<br>0<br>0                                          |

| 5 0<br>5 1<br>5 5<br>5 6 | MASK   |                                                      |

| Table 5   | ALU | Logic | Mode | Functions | (C, |

|-----------|-----|-------|------|-----------|-----|

| Irrelevan | ()  |       |      |           |     |

|           |     | 1.000 |      |           |     |

#### **Pin Definitions**

- A<sub>0-3</sub> The four address inputs to the register stack used to select one register whose contents are displayed through the A port.

- B<sub>0-3</sub> The four address inputs to the register stack used to select one register whose contents are displayed through the B port and into which new data can be written when the clock goes LOW.

- $I_{0.8}$  The nine instruction control lines to the Am2901, used to determine what data sources will be applied to the ALU ( $I_{0,1,2}$ ), what functions the ALU will perform ( $I_{3,4,5}$ ), and what data is to be deposited in the Q register or the register stack ( $I_{6,7,8}$ ).

- O<sub>3</sub>, A shift line at the MSB of the Q register (Q<sub>3</sub>) and the RAM<sub>3</sub> register stack (RAM<sub>3</sub>). Electrically these lines are three-state RAM<sub>3</sub> outputs connected to TTL inputs internal to the Am2901. When the destination code on I<sub>6,7,8</sub> indicates an up shift (octal 6 or 7), the three-state outputs are enabled and the MSB of the Q register is available on the Q<sub>3</sub> pin and the MSB of the ALU output is available on the RAM<sub>3</sub> pin. Otherwise, the three-state outputs are OFF (high-impedance) and the pins are electrically LS-TTL inputs. When the destination code calls for a down shift, the pins are used as the data inputs to the MSB of the Q register (octal 4) and RAM (octal 4 or 5).

- $O_0$ , Shift lines like  $Q_3$  and RAM<sub>8</sub>, but at the LSB of the Q register and RAM. These pins are tied to the  $Q_3$  and RAM<sub>3</sub> pins of the RAM<sub>0</sub> adjacent device to transfer data between devices for up and down shifts of the Q register and ALU data.

- $D_{0\sim3}$  Direct data inputs. A 4-bit data field which may be selected as one of the ALU data sources for entering data into the Am2901.  $D_0$  is the LSB.

- $Y_{0-3}$  The four data outputs of the Am2901. These are three-state output lines. When enabled, they display either the four outputs of the ALU or the data on the A port of the register stack, as determined by the destination code  $I_{6,7,8}$ .

- OE Output enable. When OE is HIGH, the Y outputs are OFF; when OE is LOW, the Y outputs are active (HIGH or LOW).

- P, G The carry generate and propagate outputs of the Am2901's ALU. These signals are used with the Am2902 for carry-lookahead. See Table 7 for the logic equations.

- OVR Overflow. This pin is logically the Exclusive-OR of the carry-in and carry-out of the MSB of the ALU. At the most significant end of the word, this pin indicates that the result of an arithmetic 2's complement operation has overflowed into the sign bit. See Table 7 for logic equation.

- F = 0 This is an open-collector output which goes **HIGH** (OFF) if the four ALU outputs  $F_{0-3}$  are all LOW. In positive logic, it indicates the result of an ALU operation is 0.

- $C_n$  The carry-in to the Am2901's ALU.

- $C_{n+4}$  The carry-out of the Am2901's ALU. See Table 7 for equations.

- CP The clock to the Am2901. The Q register and register stack outputs change on the clock LOW-to-

| $O_{C}$ | ial.    | $C_{u} = 0 (L)$  | OW)       | $C_n = 1$ (HIGH) |           |  |

|---------|---------|------------------|-----------|------------------|-----------|--|

|         | I 2.1.0 | Group            | Function  | Group            | Function  |  |

| 0       | 0       |                  | A + Q     |                  | A + Q + 1 |  |

| 0       | 1       | ADD              | A + B     | ADD plus         | A + B + 1 |  |

| 0       | 5       |                  | D + A     | one              | D + A + 1 |  |

| 0       | 6       |                  | D + Q     |                  | D + Q + 1 |  |

| 0       | 2       |                  | Q         |                  | Q + 1     |  |

| 0       | 3       | PASS             | в         | Increment        | B + 1     |  |

| 0       | 4       |                  | A         |                  | A + 1     |  |

| 0       | 7       |                  | D         |                  | D + 1     |  |

| 1       | 2       |                  | Q - 1     |                  | Q         |  |

| 1       | 3       | Decrement        | B – 1     | PASS             | в         |  |

| 1       | 4       |                  | A – 1     |                  | A         |  |

| 2       | 7       |                  | D – 1     |                  | D         |  |

| 2       | 2       |                  | -Q - 1    |                  | -Q        |  |

| 2       | 3       | 1's complement   | -B - 1    | 2's complement   | -B        |  |

| 2       | 4       |                  | -A - 1    | (negate)         | -A        |  |

| 1       | 7       |                  | -D - 1    |                  | -D        |  |

| 1       | 0       |                  | Q - A - 1 |                  | Q – A     |  |

| 1       | 1       | Subtract         | B – A – 1 | Subtract         | B – A     |  |

| 1       | 5       | (1's complement) | A – D – 1 | (2's complement) | A - D     |  |

| 1       | 6       |                  | Q - D - 1 |                  | Q - D     |  |

| 2       | 0       |                  | A – Q – 1 |                  | A – Q     |  |

| 2       | 1       |                  | A – B – 1 |                  | A – B     |  |

| 2       | 5       |                  | D – A – 1 |                  | D – A     |  |

| 2       | 6       |                  | D – Q – 1 |                  | D – Q     |  |

| Definit                | ions (+ = 0)   | R)                                                                             |                                                                                                                                                         |                                                                                    |                                                                              |  |  |

|------------------------|----------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|

| $P_1 = R$<br>$P_2 = R$ | + S,<br>2 + S2 | G <sub>1</sub> = R <sub>1</sub> S <sub>1</sub> C <sub>3</sub> = G <sub>2</sub> | $+ P_{9}G_{2} + P_{9}P_{2}G_{1} + P_{9}P_{2}P_{1}G_{9} + P_{9}P_{2}$<br>$+ P_{2}G_{1} + P_{2}P_{2}G_{0} + P_{9}P_{3}P_{0}C_{0}$                         | P <sub>1</sub> P <sub>0</sub> C                                                    |                                                                              |  |  |

| I <sub>5,4,3</sub>     | Function       | $\overline{P}$                                                                 | ā                                                                                                                                                       | C 8+4                                                                              | OVR                                                                          |  |  |

| 0                      | R + S          | P <sub>3</sub> P <sub>3</sub> P <sub>1</sub> P <sub>0</sub>                    | $\overline{G}_3 + \overline{P}_3\overline{G}_2 + \overline{P}_3\overline{P}_2\overline{G}_1 + \overline{P}_3\overline{P}_2\overline{P}_1\overline{G}_0$ | C.4                                                                                | $C_3 \lor C_4$                                                               |  |  |

| 1                      | S – R          | Same as R + S equations, but substitute R, for R, in definitions               |                                                                                                                                                         |                                                                                    |                                                                              |  |  |

| 2                      | R – S          | £                                                                              | - Same as R + S equations, but s                                                                                                                        | ubstitute S; for S; in definition                                                  | s                                                                            |  |  |

| 3                      | RVS            | LOW                                                                            | P,P,P,P,                                                                                                                                                | $\overline{P_0P_2P_1P_0} + C_n$                                                    | P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub> + C <sub>n</sub> |  |  |

| 4                      | R ∧ S          | LOW                                                                            | $\overline{G}_2 + \overline{G}_2 + \overline{G}_1 + \overline{G}_0$                                                                                     | $G_3 + G_2 + G_1 + G_0 + C_n$                                                      | $G_3 + G_2 + G_1 + G_0 + C_1$                                                |  |  |

| 5                      | <b>R</b> ∧ S   | LOW                                                                            | Same as R A S equat                                                                                                                                     | tions, but substitute R; for R; i                                                  | n definitions                                                                |  |  |

| 6                      | R⊹⊬S           | Same as R ∨ S, but substitute R, for R, in definitions                         |                                                                                                                                                         |                                                                                    |                                                                              |  |  |

| 7                      | R₩S            | $G_3 + G_2 + G_1 + G_0$                                                        | $\mathbf{G}_3 + \mathbf{P}_3\mathbf{G}_2 + \mathbf{P}_3\mathbf{P}_2\mathbf{G}_1 + \mathbf{P}_3\mathbf{P}_2\mathbf{P}_1\mathbf{G}_0$                     | $\frac{\overline{G_3 + P_3G_2 + P_3P_2G_1}}{+ P_3P_3P_1P_3(G_3 + \overline{C}_3)}$ | See note                                                                     |  |  |

Note:  $(\overline{P}_2 + \overline{G}_2\overline{P}_1 + \overline{G}_2\overline{G}_1\overline{P}_2 + \overline{G}_2\overline{G}_1\overline{G}_2C_2) \downarrow \downarrow (\overline{P}_3 + \overline{G}_2\overline{P}_2 + \overline{G}_2\overline{G}_2\overline{P}_1 + \overline{G}_2\overline{G}_2\overline{G}_1\overline{P}_2 + \overline{G}_2\overline{G}_2\overline{G}_1\overline{G}_2C_2)$

HIGH transition. The clock LOW time is internally the write enable to the  $16 \times 4$  RAM which comprises the "master" latches of the register stack. While the clock is LOW, the "slave" latches on the RAM outputs are closed, storing the data previously on the RAM outputs. This allows synchronous master-slave operation of the register stack.

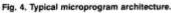

#### Expansion of The Am2901

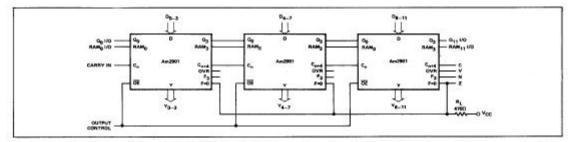

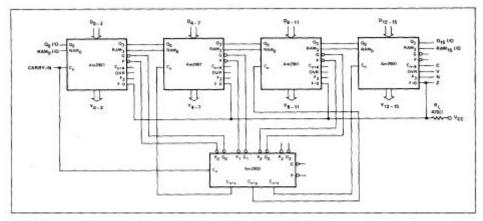

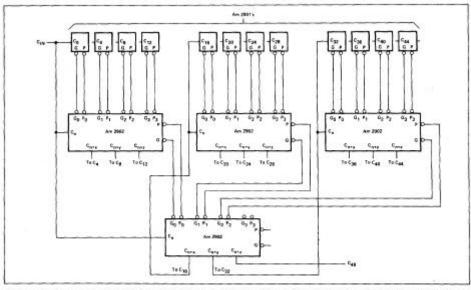

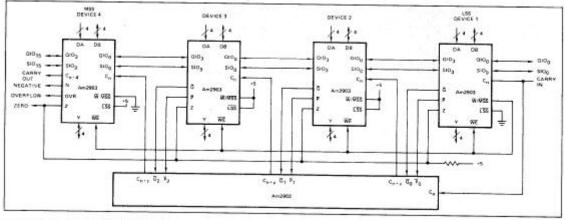

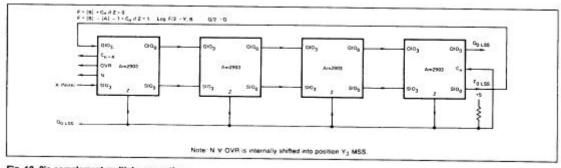

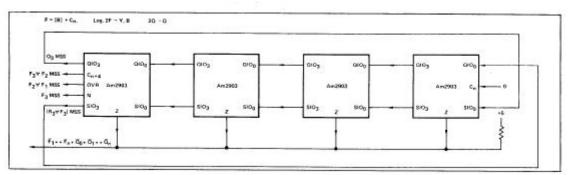

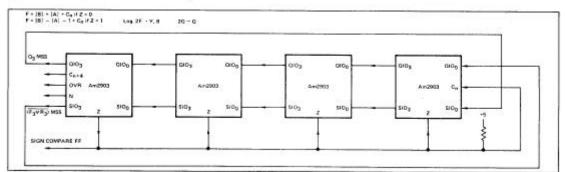

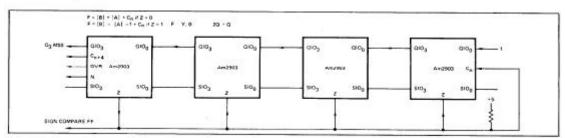

Any number of Am2901's can be interconnected to form CPU's of 12, 16, 24, 36, or more bits, in 4-bit increments. Figure 4 illustrates the interconnection of three Am2901's to form a 12-hit CPU, using ripple carry. Figure 5 illustrates a 16-bit CPU using carry lookahead, and Fig. 6 is the general carry lookahead scheme for long words.

With the exception of the carry interconnection, all expansion schemes are the same. The  $Q_3$  and RAM<sub>3</sub> pins are bidirectional left/right shift lines at the MSB of the device. For all devices except the most significant, these lines are connected to the  $Q_0$  and RAM<sub>0</sub> pins of the adjacent more significant device. These connections allow the Q registers of all Am290 l's to be shifted left or right as a contiguous n-bit register, and also allow the ALU output data to be shifted

left or right as a contiguous n-bit word prior to storage in the RAM. At the LSB and MSB of the CPU, the shift pins should be connected to three-state multiplexers which can be controlled by the microcode to select the appropriate input signals to the shift inputs. (See Fig. 7.)

The open-collector F = 0 outputs of all the Am2901's are connected together and to a pull-up resistor. This line will go HIGH if and only if the output of the ALU contains all zeros. Most systems will use this line as the Z (zero) bit of the processor status word.

The overflow and  $F'_8$  pins are generally used only at the most significant end of the array, and are meaningful only when 2's complement signed arithmetic is used. The overflow pin is the Exclusive-OR of the carry-in and carry-out of the sign bit (MSB). It will go HIGH when the result of an arithmetic operation is a number requiring more bits than are available, causing the sign bit to be erroneous. This is the overflow (V) bit of the processor status word. The F<sub>8</sub> pin is the MSB of the ALU output. It is the sign of the result in 2's complement notation, and should be used as the negative (N) bit of the processor status word.

The carry-out from the most significant Am2901 ( $C_{n+4}$  pin) is the carry-out from the array, and is used as the carry (C) bit of the processor status word.

Carry interconnections between devices may use either ripple carry or carry lookahead. For ripple carry, the carry-out  $(C_{n+4})$  of each device is connected to the carry-in  $(C_n)$  of the next more significant device. Carry lookahead uses the Am2901 lookahead carry generator. The scheme is identical with that used with the 74181/74182. Figures 5 and 6 illustrate single- and multiple-level lookahead.

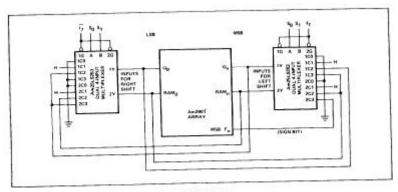

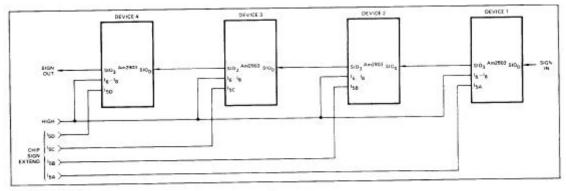

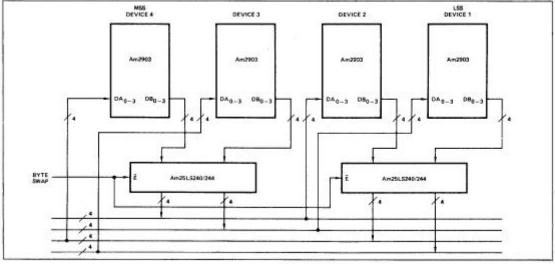

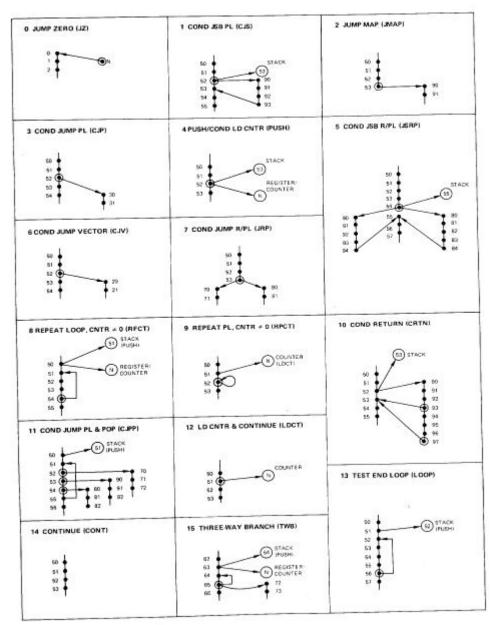

### Shift I/O Lines at the End of the Array

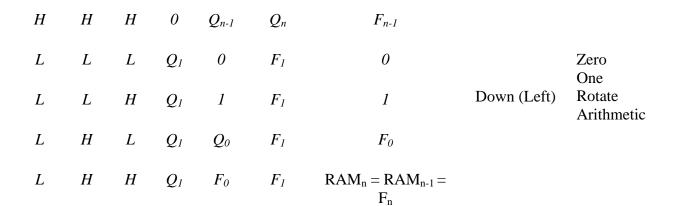

The Q-register and RAM left/right shift data transfers occur between devices over bidirectional lines. At the ends of the array, three-state multiplexers are used to select what the new inputs to the registers should be during shifting. Figure 7 shows two Am25LS253 dual four-input multiplexers connected to provide four shift modes. Instruction bit 17 (from the Am2901) is used to select whether the left-shift multiplexer or the right-shift multiplexer is active. (See Table 8.) The four shift modes in this example are:

- Zero A LOW is shifted into the MSB of the RAM on a down shift. If the Q register is also shifted then a LOW is deposited in the Q-register MSB. If the RAM or both registers are shifted up LOWs are placed in the LSBs.

- One Same as zero but a HIGH level is deposited in the LSB or MSB.

- Rotate A single-precision rotate. The RAM MSB shifts into the LSB on a right shift and the LSB shifts into the MSB on a left shift. The Q register if shifted, will rotate in the same manner.

Fig. 4. Three Am2901's used to construct 12-bit CPU with ripple carry. Corresponding A, B, and 1 pins on all devices are connected together.

Fig. 5. Four Am2901's in a 16-bit CPU using the Am2902 for carry lookahead.

Fig. 6. Carry lookahead scheme for 48-bit CPU using 12 Am2901's. The carry-out flag (C48) should be taken from the lower Am2902 rather than the right-most Am2901 for higher speed.

Fig. 7. Three-state multiplexers-used on shift I/O lines.

Arithmetic A double-length arithmetic shift if Q is also shifted. On an up shift a zero is loaded into the Q-register LSB and the Q-register MSB is loaded into the RAM LSB. On a down shift, the RAM LSB is loaded into the Q-register MSB and the ALU output MSB ( $F_n$ , the sign bit) is loaded into the RAM MSB. (This same bit will also be in the next less significant RAM bit.)

#### Hardware Multiplication

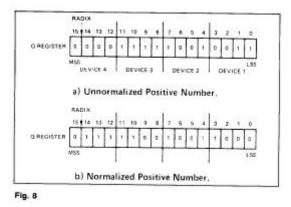

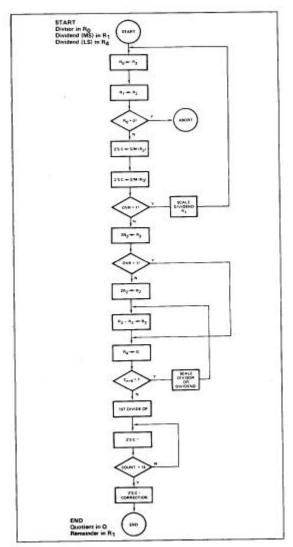

Figure 8 illustrates the interconnections for a hardware multiplication using the Am2901. The system shown uses two devices for  $8 \times 8$  multiplication, but the expansion to more bits is simple- the significant connections are at the LSB and MSB only.

The basic technique used is the "add and shift" algorithm. One clock cycle is required for each bit of the multiplier. On each cycle, the LSB of the multiplier is examined; if it is a 1, then the multiplicand is added to the partial product to generate a new partial product. The partial product is then shifted one place toward the LSB, and the multiplier is also shifted one place toward the LSB. The old LSB of the multiplier is discarded. The cycle is then repeated on the new LSB of the multiplier available at  $Q_0$ .

The multiplier is in the Am2901 Q register. The multiplicand is in one of the registers in the register stack,  $R_a$ . The product will be developed in another of the registers in the stack,  $R_b$ .

The A address inputs are used to address the multiplicand in  $R_a$ , and the B address inputs are used to address the partial product in  $R_b$ . On each cycle,  $R_a$  is conditionally added to  $R_b$ , depending on the LSB of Q as read from the  $Q_0$  output, and both the Q and the ALU output are shifted left one place. The instruction lines to the Am2901 on every cycle will be:

$I_{8,7,6} = 4$  (shift register stack input and Q register left)  $I_{5,4,3} = 0$  (Add)  $I_{2,1,0} = 1$  or 3 (select A, B or O, B as ALU sources)

Figure 8 shows the connections for multiplication. The circled numbers refer to the paragraphs below.

1 The adjacent pins of the Q register and RAM shifters are connected together so that the Q registers of both (or all) Am2901's shift left or right as a unit. Similarly, the entire

#### Table 8

| Code  | Source of new data |       |                |           |         |           |            | Type                 |

|-------|--------------------|-------|----------------|-----------|---------|-----------|------------|----------------------|

| $I_7$ | $\mathbf{S}_1$     | $S_0$ | $\mathbf{Q}_0$ | Qn        | $RAM_0$ | $RAM_n$   | Shift      |                      |

| Н     | L                  | L     | 0              | $Q_{n-1}$ | 0       | $F_{n-1}$ |            | Zero<br>One          |

| Н     | L                  | Н     | 1              | $Q_{n-1}$ | 1       | $F_{n-1}$ |            | Rotate<br>Arithmetic |

| Н     | H                  | L     | $Q_n$          | $Q_{n-1}$ | $F_n$   | $F_{n-1}$ | Up (Right) |                      |

Fig. 8. Interconnection for dedicated multiplication (8 by 8 bit) (corresponding A, B, and I connected together).

8-bit (or more) ALU output can be shifted as a unit prior to storage in the register stack.

2 The shift output at the LSB of the Q register determines whether the ALU source operands will be A and B (add multiplicand to partial product) or 0 and B (add nothing to partial product). Instruction bit  $I_1$  can select between A,. B or 0, B as the source operands; it can be driven directly from the complement of the LSB of the multiplier.

3 As the new partial product appears at the input to the register stack, it is shifted left by the RAM shifter. The new LSB of the partial product, which is complete and will not be affected by future operations, is available on the  $RAM_0$  pin. This signal is returned to the MSB of the Q register. On each cycle then, the just-completed LSB of the product is deposited in the MSB of the Q register; the Q register fills with the least significant half of the product.

4 As the ALU output is shifted down on each cycle, the sign bit of the new partial product should be inserted in the RAM MSB shift input. The F<sub>3</sub> flag will be the correct sign of the partial product unless overflow has occurred. If over-flow occurs during an addition or subtraction, the OVR flag will go HIGH and F<sub>3</sub> is not the sign of the result. The sign of the result must then be the complement of F<sub>3</sub>. The correct sign bit to shift into the MSB of the partial product is therefore  $\underline{F_3} \oplus OVR$ ; that is, F<sub>3</sub> if overflow has not occurred and F<sub>3</sub> if overflow has occurred. On the last cycle, when the MSB of the multiplier is examined, a conditional subtraction rather than addition should be performed, because the sign bit of the multiplier carries negative rather than positive arithmetic weight.

$Y = -Y_1 2^i + Y_{i\text{-}1} 2^{i\text{-}1} + .. + Y_0 2^0$

This scheme will produce a correct 2's complement product for all multiplicands and multipliers in 2's complement notation.

Figure 9 is a table showing the input states of the Am2901's for each step of a signed 2's complement multiplication.

#### Am2909 Microprogram Sequencer

#### **General Description**

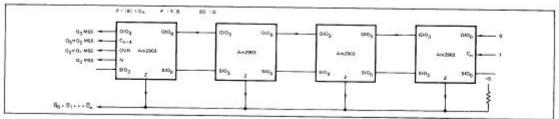

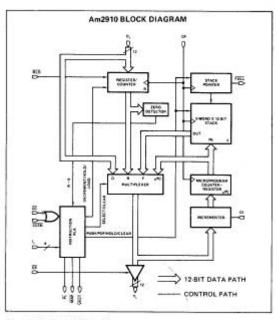

The Am2909 is a 4-bit-wide address controller intended for sequencing through a series of microinstructions contained in a ROM or PROM. Two Am2909's may be interconnected to generate an 8-bit address (256 words), and three may be used to generate a 12-bit address (4096 words). Figure 10 is a block diagram of the Am2909.

The Am2909 can select an address from any of four sources. They are: (1) a set of external direct inputs (D); (2) external data from the R inputs, stored in an internal register; (3) a 4-word-deep

| Initial Reg<br>R       | 2220 |                      | -                          |                 |       | 4m2901 | i Milen | hose                |        |       | Final Register States<br>R |                                            |                  |    |    |

|------------------------|------|----------------------|----------------------------|-----------------|-------|--------|---------|---------------------|--------|-------|----------------------------|--------------------------------------------|------------------|----|----|

| 0 Multip<br>1 Multip   |      | -                    | Program 2's Comp. Multiply |                 |       |        |         |                     | 0      |       |                            |                                            |                  |    |    |

| 2 X<br>3 X             |      | -                    | De                         | Dete8/5/75ByJ.S |       |        |         |                     |        |       |                            | Multiplicand<br>LSH Product<br>MSH Product |                  |    |    |

| 8. F                   | D    | Description          | Repeat                     |                 | - N.  |        |         | Pin                 | States | Octal | 1                          |                                            |                  | Ju | mp |

| <b>3</b> ,1            |      | Description          | repeat                     | A               | 8     | 1876   | 1543    | I210                | C.     | 00    | 03                         | RAMo                                       | RAM <sub>3</sub> | Te | 11 |

| OVA                    | 0    | Move Multiplier to Q | -                          | 0               | x     | 0      | 3       | 4                   | х      | ×     | ×                          | ×                                          | ×                |    |    |

| 0 A B                  | 8    | Clear R <sub>3</sub> | -                          | ×               | 3     | 2      | 4       | 3                   | ×      | x     | x                          | ×                                          | ×                |    |    |

| (D+B)/2<br>(A+B)/2     | B    | Cond. Add & SNH      | n-1                        | 1               | 3     | 4      | 0       | 1 or 3<br>11 + Q0LO | 0      | -     | RAMo                       | -                                          | F3YOVR           |    |    |

| (B - O)/2<br>(B - A)/2 | 8    | Cond. Subt. & Shift  | 194                        | 1               | 3     | 4      | 1       | 1 or 3<br>I1 = QpLO | 1      | 340   | RAMo                       | -                                          | F3VOVR           |    |    |

| ٥va                    | 8    | Move LSH Prod. to Rg | -                          | x               | 2     | 2      | 3       | 2                   | х      | x     | ×                          | x                                          | ×                |    |    |

|                        |      | X + De               | n's Care                   | s               | - 500 | rce.   |         | Function            |        | D - D | Intination                 |                                            |                  |    |    |

Fig. 9

push/pop stack; or (4) a program counter register (which usually contains the last address plus one). The push/pop stack includes certain control lines so that it can efficiently execute nested subroutine linkages. Each of the four outputs can be ORed with an external input for conditional skip or branch instructions, and a separate line forces the outputs to all zeros. The outputs are three-state.

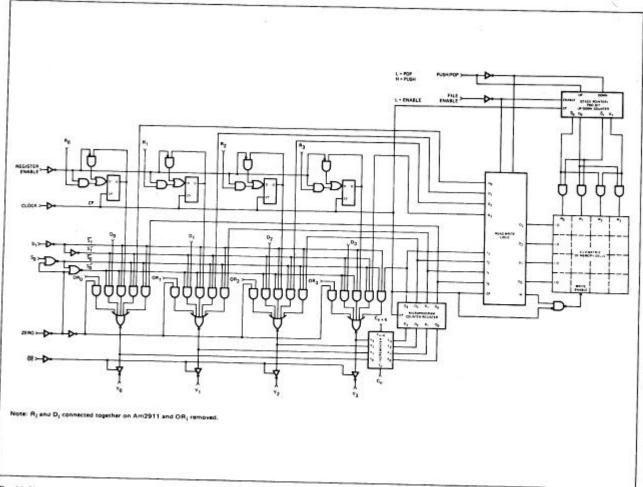

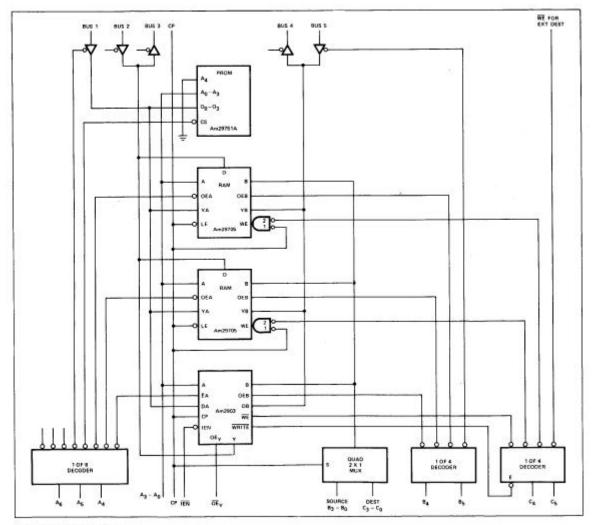

### Architecture of the Am2909

A detailed logic diagram is shown in Fig. 11. The device contains a four-input multiplexer that is used to select either the address register, direct inputs, microprogram counter, or file as the source of the next microinstruction address. This multiplexer is con trolled by the  $S_0$  and  $S_1$  inputs.

The address register consists of four *D-type*, edge-triggered flip-flops with a common clock enable. When the address register enable is LOW, new data is entered into the register on the clock LOW-to-HIGH transition. The address register is available at the multiplexer as a

source for the next microinstruction address. The direct input is a 4-bit field of inputs to the multiplexer and can be selected as the next microinstruction address.

The Am2909 contains a microprogram counter ( $\mu$  PC) that is composed of a 4-bit incrementer followed by a 4-bit register. The incrementer has carry-in (C<sub>n</sub>) and carry-out (C<sub>n+4</sub>) such that cascading to larger word lengths is straightforward. The  $\mu$  PC can be used in either of two ways. When the least significant carry-in to the increment is HIGH, the microprogram register is loaded on the next clock cycle with the current Y output word plus one ( $Y + 1 \rightarrow \mu$  PC). Thus sequential microinstructions can be executed. If this least significant C<sub>0</sub> is LOW, the incrementer passes the Y output word unmodified and the micro program register is loaded with the same Y word on the next cycle ( $Y \rightarrow \mu$  PC). Thus, the same microinstruction can be executed any number of times by using the least significant C<sub>n</sub> as the control.

Fig. 10. Microprogram sequencer block diagram.

The last source available at the multiplexer input is the  $4 \times 4$  file (stack). The file is used to provide return address linkage when executing microsubroutines. The file contains a built-in stack pointer (SP) which always points to the last file word written. This allows stack reference operations (looping) to be performed without a push or pop.

The stack pointer operates as an up/down counter with separate push/pop and file enable inputs. When the file enable input is LOW and the push/pop input is HIGH, the PUSH operation is enabled. This causes the stack pointer to increment and the file to be written with the required return linkage-the next microinstruction address following the subroutine jump which initiated the PUSH.

If the file enable input is LOW and the push/pop control is LOW, a POP operation occurs. This implies the usage of the return linkage during this cycle and thus a return from subroutine. The next LOW-to-HIGH clock transition causes the stack pointer to decrement. If the file enable is HIGH, no action is taken by the stack pointer regardless of any other input.

The stack pointer linkage is such that any combination of pushes, pops, and stack references can be achieved. One microinstruction subroutines can be performed. Since the stack is 4 words deep, up to four microsubroutines can be nested.

The ZERO input is used to force the four outputs to the binary zero state. When the ZERO input is LOW, all Y outputs are LOW regardless of any other inputs (except OE). Each Y output bit also has a separate OR input such that a conditional logic 1 can be forced at each Y output. This allows jumping to different microinstructions on programmed conditions.

The Am2909 features three-state *Y* outputs. These can be particularly useful in military designs requiring external ground support equipment (GSE) to provide automatic checkout of the microprocessor. The internal control can be placed in the high-impedance state, and preprogrammed sequences of micro instructions can be executed via external access to the control ROM/PROM.

# Definition of Terms

A set of symbols is used to represent various internal and external registers and signals used with the Am2909. Since its principal

Fig. 11. Microprogram sequencer block diagram.

181

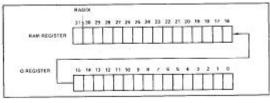

application is as a controller for a microprogram store, it is necessary to define some signals associated with the microcode itself. Figure 12 illustrates the basic interconnection of

Am2909, memory, and microinstruction register. The definitions here apply to this architecture.

# Inputs to Am2909

| <u>S<sub>1</sub>,</u> S <sub>0</sub> | Control lines for address source selection.                             |

|--------------------------------------|-------------------------------------------------------------------------|

| <u>FE,</u> PUP                       | Control lines for push/pop stack.                                       |

| RE                                   | Enable line for internal address register.                              |

| <u>OR</u> <sub>i</sub>               | Logic OR inputs on each address output line.                            |

| ZERO                                 | Logic AND input on the output lines.                                    |

| OE                                   | Output enable. When OE is HIGH, the Y outputs are OFF (high impedance). |

| C <sub>n</sub>                       | Carry-in to the incrementer.                                            |

| $R_i$                                | Inputs to the internal address register.                                |

| D <sub>i</sub>                       | Direct inputs to the multiplexer.                                       |

| СР                                   | Clock input to the AR and $\mu$ PC register and push-pop stack.         |

# Outputs from the Am2909

- Y<sub>i</sub> Address outputs from Am2909 (address inputs to control memory).

- $C_{n+4}$  Carry-out from the incrementer.

# Internal Signals

$\mu$  PC Contents of the microprogram counter.

- REG Contents of the register.

- STK0-STK3 Contents of the push/pop stack. By definition, the word in the 4 ×4 file addressed by the stack pointer is STK0. Conceptually data is pushed into the stack at STK0; a subsequent push moves STK0 to STK1; a pop implies STK3 → STK2 → STK1 → STK0. Physically, only the stack pointer changes when a push or pop is performed. The data does not move. I/O occurs at STK0.

- SP Contents of the stack pointer.

#### External to the Am2909

- A Address to the control memory.

- I(A) Instruction in control memory at address A.

- $\mu$  Contents of the microword register (at output of control memory). The microword register WR contains the instruction currently being executed.

- $T_n$  Time period (cycle) n.

### **Operation of the Am2909**

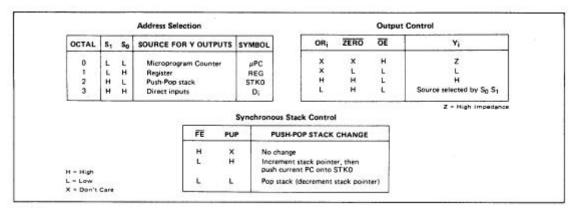

Figure 13 lists the select codes for the multiplexer. The two bits applied from the microword register (and additional combinational logic for branching) determine which data source contains the

Fig. 12. Microprogram sequencer control.

address for the next microinstruction. The contents of the selected source will appear on the Y outputs. Figure 13 also shows the truth table for the output control and for the control of the push/pop stack. Table 9 shows in detail the effect of  $S_0$ ,  $S_1$ , FE, and PUP on the Am2909. These four signals define what address appears on the Y outputs and what the state of all the internal registers will be following the clock LOW-to-HIGH edge. In this illustration, the

microprogram counter is assumed to contain initially some word J, the address register some word K, and the four words in the push/pop stack  $\mathbf{R}_{a}$  through  $R_{d}$ .

Figure 14 illustrates the execution of a subroutine using the Am2909. The configuration of Fig. 11 is assumed. The instruction being executed at any given time is the one contained in the microword register ( $\mu$  WR). The contents of the  $\mu$  WR also control (indirectly, perhaps) the four signals S<sub>0</sub>, S<sub>1</sub>, FE, and PUP. The starting address of the subroutine is applied to the D inputs of the Am2909 at the appropriate time.

In the columns on the left is the sequence of microinstructions to be executed. At address J + 2, the sequence control portion of the microinstruction contains the command "Jump to subroutine at A." At the time T<sub>2</sub>, this is in the  $\mu$  WR, and the Am2909 inputs are set up to execute the jump and save the return address. The subroutine address **A** is applied to the D inputs from the  $\mu$  WR and appears on the Y outputs. The first instruction of the subroutine, I(A), is accessed and is at the inputs of the  $\mu$  WR. On the next clock transition, I(A) is loaded into the  $\mu$  WR for execution, and the return address J + 3 is pushed onto the stack. The return instruction is executed at T<sub>5</sub>.

# Table 9 Output and Internal Next-Cycle Register States for Am2909

| Cycle | <i>S</i> <sub>1</sub> , <i>S</i> <sub>0</sub> , <i>FE</i> , <i>PUP</i> | μPC   | REG | STK0 | STKI | STK2 | STK3 | $Y_{OUT}$ | Comment                  | Principal use |

|-------|------------------------------------------------------------------------|-------|-----|------|------|------|------|-----------|--------------------------|---------------|

| Ν     | 0000                                                                   | J     | K   | Ra   | Rb   | Rc   | Rd   | J         | Pop stack                | End<br>loop   |

| N+1   |                                                                        | J+1   | K   | Rb   | Rc   | Rd   | Ra   |           |                          | 100p          |

| Ν     | 0001                                                                   | J     | K   | Ra   | Rb   | Rc   | Rd   | J         | Push µ PC                | Setup         |

| N +1  |                                                                        | J +1  | K   | J    | Ra   | Rb   | Rc   |           |                          | loop          |

| Ν     | 0 0 1 X                                                                | J     | K   | Ra   | Rb   | Rc   | Rd   | J         | Continue                 | Continue      |

| N+1   |                                                                        | J+1   | K   | Ra   | Rb   | Rc   | Rd   |           |                          |               |

| Ν     | 0100                                                                   | J     | Κ   | Ra   | Rb   | Rc   | Rd   | Κ         | Pop stack;               | End           |

| N + 1 |                                                                        | K+ 1  | K   | Rb   | Rc   | Rd   | Ra   |           | Use AR for address       | loop          |

| Ν     | 0101                                                                   | J     | Κ   | Ra   | Rb   | Rc   | Rd   | Κ         | Push µ PC;               | JSR AR        |

| N + 1 |                                                                        | K+ 1  | K   | J    | Ra   | Rb   | Rc   |           | Jump to address in AR    |               |

| Ν     | 0 1 1 X                                                                | J     | K   | Ra   | Rb   | Rc   | Rd   | Κ         | Jump to address in AR    | JMP AR        |

| N+ 1  |                                                                        | K + 1 | K   | Ra   | Rb   | Rc   | Rd   |           |                          |               |

| Ν     | 1000                                                                   | J     | Κ   | Ra   | Rb   | Rc   | Rd   | Ra        | Jump to address in STK0; | RTS           |

| N+1   |                                                                        | Ra+1  | K   | Rb   | Rc   | Rd   | Rc   |           | Pop stack                |               |

| Ν     | 1001 | J        | Κ | Ra | Rb | Rc | Rd | R  | Jump to address in STK0; |           |

|-------|------|----------|---|----|----|----|----|----|--------------------------|-----------|

| N+1   |      | Ra+1     | K | J  | Ra | Rb | Ra |    | Push µ PC                |           |

| Ν     | 101X | J        | K | Ra | Rb | Rc | Rd | Ra | Jump to address in STK0  | Stack ref |

| N + 1 |      | Ra+<br>1 | K | Ra | Rb | Rc | Rd |    |                          | (loop)    |

| Ν     | 1100 | J        | K | Ra | Rb | Rc | Rd | D  | Pop stack;               | End       |

| N +1  |      | D+1      | K | Rb | Rc | Rd | Ra |    | Jump to address on D     | loop      |

| Ν     | 1101 | J        | Κ | Ra | Rb | Rc | Rd | D  | Jump to address on D     | JSR D     |

| N +1  |      | D +1     | K | J  | Ra | Rb | Rc |    | Push µ PC                |           |

| Ν     | 111X | J        | K | Ra | Rb | Rc | Rd | D  | Jump to address on D     | JMP D     |

| N +1  |      | D+1      | K | Ra | Rb | Rc | Rd |    |                          |           |

X = Don't care, 0 = LOW, 1 = HIGH, Assume  $C_n = HIGH$

Note: STK0 is the location addressed by the stack pointer.

| Execute              | Micro                         | program                  | Execute C                                                | lock                                | To                 | T,          | T2               | Т3                   | T <sub>4</sub>       | T <sub>5</sub>   | Te               | T <sub>2</sub>     | Та | To  |

|----------------------|-------------------------------|--------------------------|----------------------------------------------------------|-------------------------------------|--------------------|-------------|------------------|----------------------|----------------------|------------------|------------------|--------------------|----|-----|

| Cycle                | Address                       | Sequencer<br>Instruction | Signa                                                    | 1920                                |                    |             |                  | -                    |                      |                  |                  | Ц                  |    | - 8 |

| To<br>T1<br>T2<br>T6 | J-1<br>J<br>J+1<br>J+2<br>J+3 | -<br>JSR A               | Am2909<br>Inputs<br>(from<br>µWR)                        | S1. S0<br>FE<br>PUP<br>D            | о<br>н<br>х<br>х   | O I X X     | 3<br>L<br>H<br>A | о<br>н<br>х<br>х     | 0<br>H X<br>X        | 2<br>L<br>L<br>X | D<br>H<br>X<br>X | 0 H X X            |    |     |

| τ <sub>3</sub>       | J+4<br>-<br>-<br>-            |                          | Internal<br>Registers                                    | µPC<br>STKO<br>STK1<br>STK2<br>STK3 | J+1<br>-<br>-<br>- | <br><br>1+5 | -<br>-<br>1•3    | A+1<br>J+3<br>-<br>- | A+2<br>J+3<br>-<br>- | A+3<br>J+3<br>-  | 3+4<br><br>-     | J+5<br>-<br>-<br>- |    |     |

| T3<br>T4             | A<br>A+1                      | 1(A)<br>_                | Am2909<br>Output                                         | Y                                   | J+1                | J+2         | A                | A+1                  | A+2                  | J+3              | J+4              | J+5                |    |     |

| T <sub>5</sub>       | A+2                           | ATS -                    | ROM<br>Output                                            | (Y)                                 | 11.3+1)            | JSR A       | HA)              | I(A+1)               | RTS                  | 11J+31           | 1(J+4)           | 1(J+5)             |    |     |

|                      | -                             |                          | Contents<br>of pWR<br>(Instruction<br>being<br>executed) | µWR                                 | (JJ)               | I(J+1)      | JSR A            | I(A)                 | r(A+1)               | RTS              | 1(J+3)           | 1(")+4}            |    |     |

#### Fig. 14. Subroutine execution.

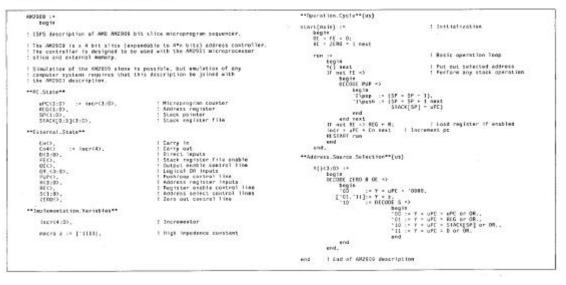

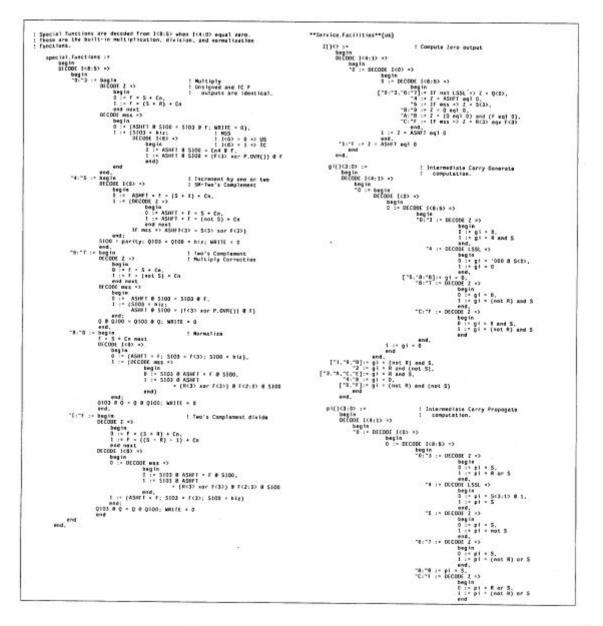

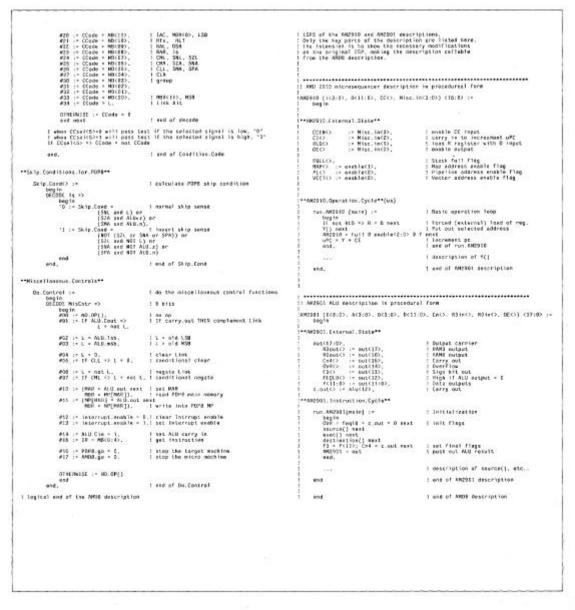

#### APPENDIX 1 AM2909 ISP DESCRIPTION

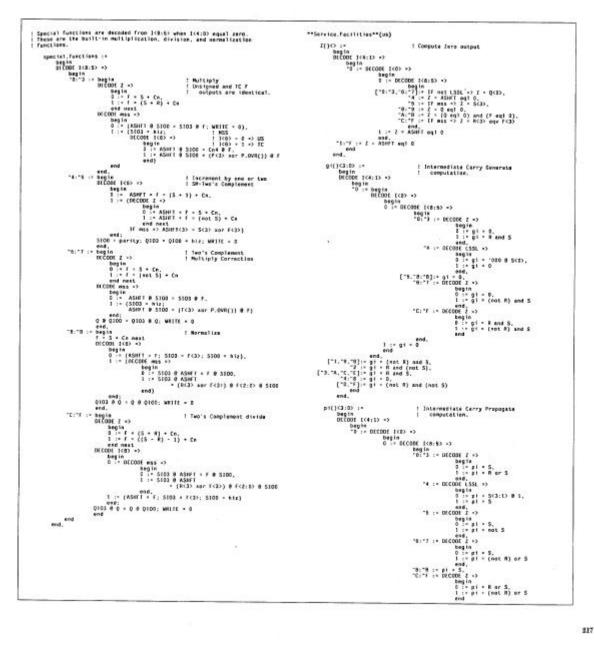

#### APPENDIX 2 AM2901 ISP DESCRIPTION

| AH2001 :-<br>Degin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | destination (*<br>begin<br>OffODE dest =>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | I Destination calculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |